-

Układ scalony pamięci

-

Czipy czujników

-

Układ scalony zasilania

-

Rezystory Kondensatory Cewki indukcyjne

-

Układ scalony mikrokontrolera

-

Złącze IC

-

Przełącz układ scalony

-

Moduł interfejsu komunikacyjnego

-

Układ scalony przekaźnika

-

Chip sterownika silnika

-

Tranzystor diodowy

-

Układ scalony konwertera danych

-

Układ scalony wzmacniacza

-

Panie PatrykuSzybka reakcja i pełne zrozumienie potrzeb klienta, dobre podejście do obsługi, zgadzamy się z twoją obsługą.

Panie PatrykuSzybka reakcja i pełne zrozumienie potrzeb klienta, dobre podejście do obsługi, zgadzamy się z twoją obsługą. -

Panie HarrisonPoważne podejście do obsługi, a także wysoka jakość produktów zasługują na zaufanie każdego.

Panie HarrisonPoważne podejście do obsługi, a także wysoka jakość produktów zasługują na zaufanie każdego. -

AniaTo doskonały zakup. Zdolność Twojej firmy do oferowania konkurencyjnych cen i produktów wysokiej jakości jest imponująca.

AniaTo doskonały zakup. Zdolność Twojej firmy do oferowania konkurencyjnych cen i produktów wysokiej jakości jest imponująca.

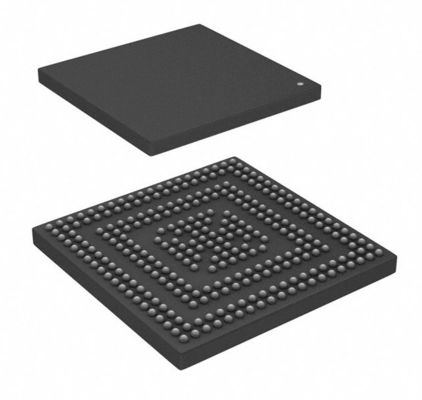

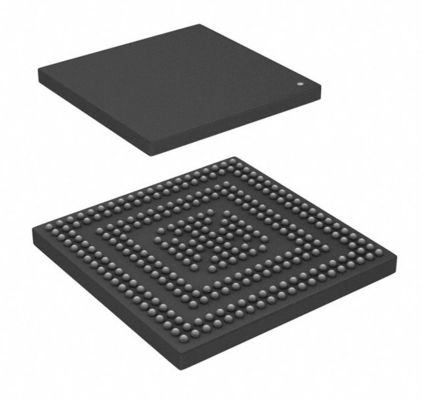

SAK-TC277TP-64F200N Dc AURIX mikrokontroler Chip Ic 32-bitowy trójrdzeniowy 200MHz 4MB 4M X 8 FLASH PG-LFBGA-292-6

Contact me for free samples and coupons.

Whatsapp:0086 18588475571

Wechat: 0086 18588475571

Skype: sales10@aixton.com

If you have any concern, we provide 24-hour online help.

x| Producent | Technologie firmy Infineon | Kategoria | Mikrokontrolery |

|---|---|---|---|

| Numer produktu | SAK-TC277TP-64F200N | Seria | Aurix |

| Stan produktu | Aktywny | Procesor rdzeniowy | TriCore™ |

| Rozmiar rdzenia | 32-bitowy trójrdzeniowy | Prędkość | 200MHz |

| Łączność | ASC, CANbus, Ethernet, FlexRay, HSSL, I²C, LINbus, MSC, PSI5, QSPI, SENT | Urządzenia peryferyjne | DMA, POR, WDT |

| Liczba wejść/wyjść | 169 | Rozmiar pamięci programu | 4 MB (4 MB x 8) |

| Typ pamięci programu | Błysk | Rozmiar pamięci EEPROM | 64K x 8 |

| Rozmiar pamięci RAM | 472K x 8 | Napięcie — zasilanie (Vcc/Vdd) | 1,17 V ~ 5,5 V |

| Konwertery danych | A/D 60x12b SAR, Sigma-Delta | Typ oscylatora | Zewnętrzny |

| temperatura robocza | -40°C ~ 125°C (TA) | Typ mocowania | Montaż powierzchniowy |

| Opakowanie / Sprawa | 292-LFBGA | Pakiet urządzeń dostawcy | PG-LFBGA-292-6 |

| Podstawowy numer produktu | TC277TP64 | ||

| High Light | sak-tc277tp-64f200n dc,układ mikrokontrolera ic,sak-tc277tp-64f200n |

||

SAK-TC277TP-64F200N TriCore™ AURIX™ Mikrokontroler IC 32-bitowy Tri-Core 200MHz 4MB (4M x 8) FLASH PG-LFBGA-292-6

Arkusz danych:SAK-TC277TP-64F200N

| Kategoria | Mikrokontrolery |

| Prod | Technologie firmy Infineon |

| Seria | AURIX |

| Stan produktu | Aktywny |

| Programowalny kluczem cyfrowym | Nie zweryfikowany |

| Procesor rdzeniowy | Trójrdzeniowy |

| Rozmiar rdzenia | 32-bitowy trójrdzeniowy |

| Prędkość | 200MHz |

| Łączność | ASC, CANbus, Ethernet, FlexRay, HSSL,I²C, LINbus, MSC, PSI5, QSPI, SENT |

| Urządzenia peryferyjne | DMA, POR, WDT |

| Liczba wejść/wyjść | 169 |

| Rozmiar pamięci programu | 4 MB (4 MB x 8) |

| Typ pamięci programu | BŁYSK |

| Rozmiar pamięci EEPROM | 64K x 8 |

| Rozmiar pamięci RAM | 472K x 8 |

| Napięcie — zasilanie (Vcc/Vdd) | 1,17 V ~ 5,5 V |

| Konwertery danych | A/D 60x12b SAR, Sigma-Delta |

| Typ oscylatora | Zewnętrzny |

| temperatura robocza | -40°C ~ 125°C (TA) |

| Typ mocowania | Montaż powierzchniowy |

| Opakowanie / etui | 292-LFBGA |

| Pakiet urządzeń dostawcy | PG-LFBGA-292-6 |

| Podstawowy numer produktu | TC277TP64 |

Podsumowanie funkcji

Rodzina produktów TC27x ma następujące cechy:

• Wysokowydajny mikrokontroler z trzema rdzeniami procesora

• Dwa 32-bitowe superskalarne procesory TriCore (TC1.6P), z których każdy ma następujące cechy:

– Doskonała wydajność w czasie rzeczywistym

– Mocna obsługa bitów

– W pełni zintegrowane możliwości DSP

– Jednostka mnożąco-akumulująca zdolna do utrzymania 2 operacji MAC na cykl

– W pełni potokowa jednostka zmiennoprzecinkowa (FPU)

– praca do 200 MHz w pełnym zakresie temperatur

– do 120 KB Data Scratch-Pad RAM (DSPR)

– do 32 Kbajtów instrukcji Scratch-Pad RAM (PSPR)

– 16 KB pamięci podręcznej instrukcji (ICACHE)

– 8 KB pamięci podręcznej danych (DCACHE)

• Energooszczędny skalarny procesor TriCore (TC1.6E), posiadający następujące cechy:

– Kompatybilność kodu binarnego z TC1.6P

– praca do 200 MHz w pełnym zakresie temperatur

– do 112 KB Data Scratch-Pad RAM (DSPR)

– do 24 Kbajtów instrukcji Scratch-Pad RAM (PSPR)

– 8 KB pamięci podręcznej instrukcji (ICACHE)

– Bufor odczytu danych 0,125 KB (DRB)

• Blokowane rdzenie cienia dla jednego TC1.6P i dla TC1.6E

• Wiele pamięci na chipie

– Wszystkie wbudowane pamięci NVM i SRAM są chronione przez ECC

– do 4 MB programowej pamięci Flash (PFLASH)

– do 384 Kbyte Data Flash Memory (DFLASH) użyteczna do emulacji EEPROM

– 32 KB pamięci (LMU)

– BootROM (BROM)

• 64-kanałowy kontroler DMA z bezpiecznym transferem danych

• Zaawansowany system przerwań (chroniony przez ECC)

• Wysokowydajna struktura magistrali na chipie

– 64-bitowy interfejs Cross Bar Interconnect (SRI) zapewniający szybki równoległy dostęp między masterami magistrali, procesorami i pamięciami

– 32-bitowa systemowa magistrala peryferyjna (SPB) dla wbudowanych w układ urządzeń peryferyjnych i jednostek funkcjonalnych

– Jeden most autobusowy (most SFI)

• Opcjonalny sprzętowy moduł bezpieczeństwa (HSM) w niektórych wariantach

• Jednostka zarządzania bezpieczeństwem (SMU) obsługująca alarmy monitora bezpieczeństwa

• Moduł testowania pamięci z funkcjami ECC, inicjalizacji pamięci i MBIST (MTU)

• Hardware I/O Monitor (IOM) do sprawdzania cyfrowych wejść/wyjść

• Wszechstronne jednostki peryferyjne na chipie

– Cztery asynchroniczne/synchroniczne kanały szeregowe (ASCLIN) ze sprzętową obsługą LIN (V1.3, V2.0, V2.1 i J2602) do 50 Mbodów

– Cztery kolejkowane kanały interfejsu SPI (QSPI) z funkcją master i slave do 50 Mbit/s

– High Speed Serial Link (HSSL) do szeregowej komunikacji między procesorami z szybkością do 320 Mbit/s

– Dwa szeregowe interfejsy Micro Second Bus (MSC) do rozbudowy portu szeregowego o zewnętrzne urządzenia zasilające

– Jeden moduł MultiCAN+ z 4 węzłami CAN i 256 dowolnie przypisywanymi obiektami komunikatów do wysokowydajnej obsługi danych poprzez buforowanie FIFO i transfer danych przez bramkę

– 10 kanałów Single Edge Nibble Transmission (SENT) do podłączenia czujników

– Jeden moduł FlexRayTM z 2 kanałami (E-Ray) obsługujący wersję 2.1

– Jeden ogólny moduł czasowy (GTM) zapewniający potężny zestaw funkcji cyfrowego filtrowania sygnału i timera w celu realizacji autonomicznego i złożonego zarządzania wejściami/wyjściami

– Jeden moduł Capture / Compare 6 (dwa jądra CCU60 i CCU61)

– Jeden uniwersalny timer z 12 jednostkami (GPT120)

– Trzykanałowy interfejs czujnika peryferyjnego zgodny z V1.3 (PSI5)

– Interfejs czujnika peryferyjnego z szeregowym PHY (PSI5-S)

– Opcjonalny interfejs Inter-Integrated Circuit Bus Interface (I2C) zgodny z V2.1

– Opcjonalny IEEE802.3 Ethernet MAC z interfejsami RMII i MII (ETH)

• Wszechstronny system sukcesywnej aproksymacji ADC (VADC)

– Klaster 8 niezależnych jąder ADC

– Zakres napięcia wejściowego od 0 V do 5,5 V (zasilanie ADC)

• Delta-Sigma ADC (DSADC) – Sześć kanałów

• Cyfrowe programowalne porty we/wy

• Wbudowana obsługa debugowania dla OCDS poziomu 1 (procesory, DMA, szyny chipowe)

• debugowanie wielordzeniowe, śledzenie w czasie rzeczywistym i kalibracja

• cztero/pięcioprzewodowy interfejs JTAG (IEEE 1149.1) lub DAP (Device Access Port)

• System zarządzania energią i wbudowane regulatory

• Jednostka generowania zegara z systemem PLL i Flexray PLL

• Wbudowany regulator napięcia

Obraz danych:

![]()

![]()